三星發(fā)布新晶體管:1nm之后的選擇?

瀏覽次數(shù):767

|

發(fā)布日期:2021-12-18

三星發(fā)布新晶體管:1nm之后的選擇?

IBM和三星聲稱他們在半導體設計方面取得了突破。

在舊金山 IEDM 會議的第一天,兩家公司宣布了一種在芯片上垂直堆疊晶體管的新設計。 對于當前的處理器和 SoC,晶體管平放在硅表面上,電流從一側流向另一側。 相比之下,垂直傳輸場效應晶體管 (VTFET) 彼此垂直,電流垂直流動。

據(jù) IBM 和三星稱,這種設計有兩個優(yōu)點。 首先,它將允許他們繞過許多性能限制并將摩爾定律擴展到 1 納米閾值之外。 更重要的是,由于電流較大,該設計減少了能源浪費。 他們估計 VTFET 將使處理器比采用 FinFET 晶體管設計的芯片快兩倍,并將功耗降低 85%。

IBM 和三星聲稱,這一過程可能有一天會讓手機一次充電使用整整一周。 他們表示,它還可以使某些能源密集型任務(包括加密采礦)更加節(jié)能,因此對環(huán)境的影響較小。

IBM 和三星尚未透露他們何時計劃將該設計商業(yè)化。 他們并不是唯一一家試圖突破 1 納米屏障的公司。 英特爾在 7 月份表示,其目標是到 2024 年完成 Angstrom 芯片的設計。該公司計劃使用其新的“英特爾 20A”節(jié)點和 RibbonFET 晶體管來完成這一壯舉。

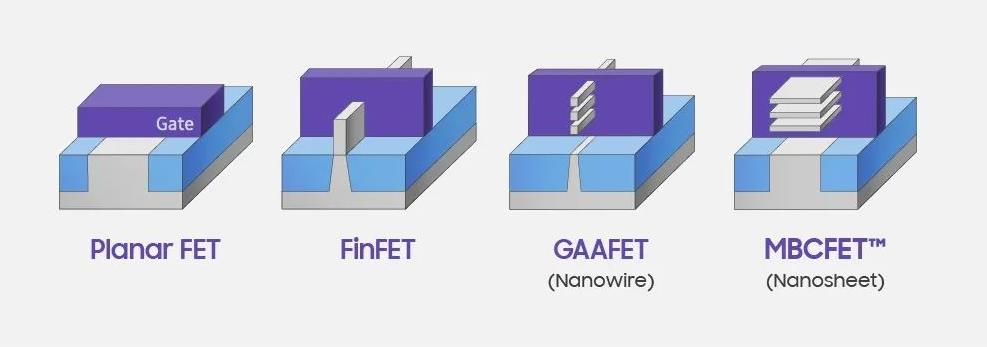

三星計劃2025年量產2nm

在先進的半導體技術方面,臺積電目前是無可爭議的領先者。 Q3占據(jù)了整整53%的代工份額。 三星排名第二,但份額僅為臺積電的1/3。 所以三星押注下一代。 工藝,包括3nm和未來的2nm工藝。 按照三星的計劃,3nm工藝將放棄FinFET晶體管技術,轉向柵極周圍的GAA。 3nm工藝分為兩個版本,其中3GAE(低功耗版)將于2022年初量產,3GAP(高性能版)將于2023年初量產。

與5nm相比,三星新推出的3nm GAA可以縮小35%的面積,同等功耗下性能提升30%,同等性能下功耗降低50%。

下一步是2nm工藝。 三星高層再次表示2nm工藝將于2025年量產。

但具體工藝指標尚未公布。 我只知道是GAA晶體管,基于MBCFET(Multi-Bridge Channel FET)技術,如3nm。 這是一種可以垂直堆疊的納米芯片晶體管,兼容當前的CMOS工藝以共享設備。 與制造方法相比,降低了新技術的升級成本。

三星的2nm工藝是一大進步,有很多創(chuàng)新亮點,與現(xiàn)有的2nm工藝不同——IBM此前在全球發(fā)布了一款2nm芯片,可以在指甲蓋大小內集成500億個晶體管,這是一個 與 7nm 工藝相比有所改進。 性能提升 45% 或功耗降低 75%,預計 2024 年量產。

三星也參與了IBM的2nm工藝,但其量產的2nm工藝與IBM的2nm工藝不一樣。 后者需要新的生產方式,三星也將依賴自家的2nm工藝。

- 上一篇 >: 因為芯片的短缺,臺晶圓廠產能被搶購一空

- 下一篇 >: IHS:汽車芯片市場規(guī)模將猛增